# Микроконтроллер Комдив—МК К5500ВК018

## ТЕХНИЧЕСКИЕ ХАРАКТЕРИСТИКИ

диапазон рабочих температур от -40 до +85°C

частота процессорного ядра до 300 МГц

напряжение питания 1.0, 1.35/1.5, 3.3B

Максимальная потребляемая мощность 0.5 Вт

технология изготовления КМОП 65 нм

корпус BGA 256 металлополимерный

размер корпуса 17х17х1.6 мм

Программное обеспечение:

- ОС РВ Багет 2.6

- библиотеки поддержки протоколов

- инструментальные средства

Микросхема К5500ВК018 — малопотребляющий микроконтроллер «Комдив-МК» на основе отечественных IP-блоков для применения в устройствах промышленного интернета вещей. Микроконтроллер включает суперскалярное 64-разрядное RISC-микропроцессорное ядро с архитектурой КОМДИВ64 и встроенные системные и периферийные контроллеры.

Микросхема К5500ВК018 предназначена для применения в качестве управляющего контроллера в автоматизации объектов ТЭК, промышленности, ЖКХ, транспорта и т.п., контроллера сбора и обработки данных в распределенных системах управления при автоматизации технологически-сложных объектов.

Основные выполняемые функции: прием информации с датчиков, в том числе аналоговых и по интерфейсам последовательной связи; нормализация измеренных величин; ПИД-регулирование; циклическое самотестирование; управление актуаторами; информационное взаимодействие с верхним управляющим уровнем.

Обширный набор периферийных контроллеров позволяет строить на основе Комдив-МК системы автоматического управления для широкого спектра применений и гибко настраивать для различных задач.

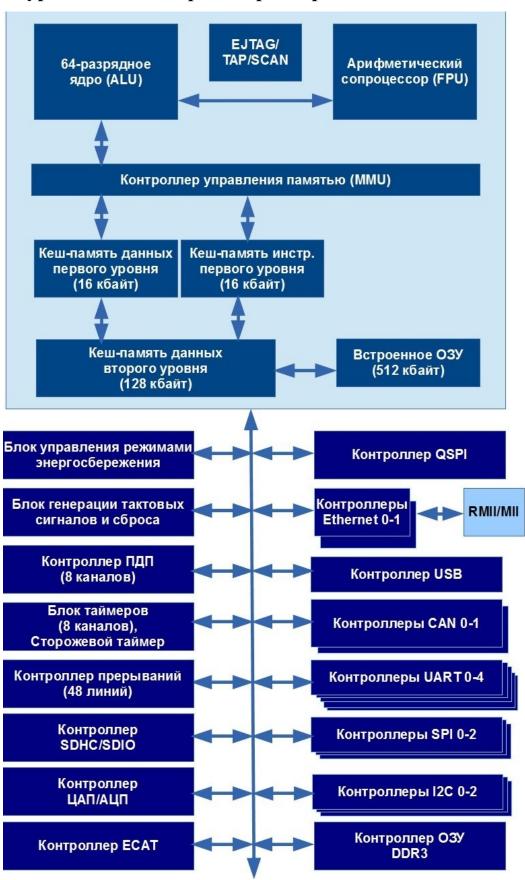

# Состав Комдив-МК

## Ядро

- 64-разрядное целочисленное ядро с архитектурой КОМДИВ64 (MIPS-совместимое);

- сопроцессор вещественной арифметики, соответствующий стандарту IEEE754, поддерживающий форматы представления вещественных чисел одинарной (32 разряда) и двойной (64 разряда) точности, а также формат «пара вещественных чисел одинарной точности»;

- ассоциативный буфер трансляции виртуальных адресов (jTLB) на 64 адреса (128 страниц);

- кэш-память данных 1-го уровня (16 кбайт) и инструкций (16 кбайт);

- общая кэш-память 2-го уровня для данных и инструкций размером 128 кбайт (4 секции);

- 128-разрядная внутренняя шина;

- 7-ступенчатый суперскалярный конвейер с предвыборкой инструкций и возможностью выполнения двух команд за такт.

#### Память

Встроенное ОЗУ статического типа объемом 512 кбайт.

## Встроенные контроллеры

## Контроллер динамической памяти

Контроллер поддерживает до 2 Гбайт синхронной динамической памяти типа DDR3/DDR3L SDRAM, при этом логическая модель контроллера памяти одинакова для DDR3 с напряжением питания 1,5 В и для DDR3L с напряжением питания 1,35 В. Разрядность шины данных 16 бит.

## Блок таймеров

Блок включает 8 однотипных независимых 64-разрядных таймеров-счётчиков и 64-разрядный сторожевой (WatchDog) таймер. Работа всех таймеров возможна также в 32-разрядном режиме. Каждый таймер -счётчик и сторожевой таймер программируется независимо, имеет программируемый предделитель частоты и работает на одной их двух частот - опорной и внешней. Отмеряемые временные интервалы от 1 такта. Типовое время срабатывания сторожевого таймера — 10 с. Любой таймер-счетчик также может быть сторожевым.

Таймеры поддерживают функции регистрации событий, режимы ШИМ и меандр.

#### МИКРОКОНТРОЛЛЕР КОМДИВ-МК К5500ВК018

#### Контроллер прерываний

Контроллер прерываний на 48 входов перераспределяет все прерывания на 10 линий запросов на прерывание процессору (используется 6 из 10 в соответствии с архитектурой ядра). Поддерживает арбитрацию одновременных запросов, которые распределены на одну линию процессора, по фиксированным приоритетам; возвращает запрограммированный вектор прерывания в соответствии с приоритетом

#### Блок регистров системного контроллера

Конфигурационные регистры системного контроллера управляют поведением системы в целом (частоты, режимы и пр.).

#### Контроллеры Ethernet

Два контроллера Ethernet поддерживают режимы 10/100 Мбит/с, полу-/ полный дуплекс; внутреннюю и внешнюю петли для диагностических целей; механизмы борьбы с блокировками канала Ethernet; управление пото-ком в соответствии со стандартом IEEE 802.3-2005; набор гибких схем адресной фильтрации входящих пакетов. Имеется интерфейс МІІ (RMII) для связи с РНУ.

## Контроллер EtherCAT

Блок контроллера содержит два порта EtherCAT, подключённых к тем же выводам, что и Ethernet.

Блок каждого из двух портов EtherCAT производит прием и передачу данных от внешней микросхемы приемопередатчика Ethernet 100 МБит/с с использованием интерфейса МІІ, управляет функционированием микросхемы приемопередатчика Ethernet по интерфейсу управления МІ (management interface).

## Контроллеры последовательных интерфейсов RS-232C

В микросхеме присутствует 5 контроллеров.

Интерфейс контроллера последовательных портов программно совместим с регистрами и логикой работы микросхемы A16450, дополненной приёмным и передающим буферами FIFO глубиной 255 байта каждый. Для мониторинга статуса заполненности буферов были введены дополнительные регистры, делящие адресное пространство со стандартными регистрами. Для ускорения доступа к дополнительным регистрам предусмотрен отключаемый режим несовместимости со стандартной программной моделью.

#### Контроллер шины І2С

В микросхеме присутствуют 3 контроллера I2C, выполняющие передачу данных на частотах 100 кГц, 400 кГц и 1 МГц. Контроллеры позволяют работать в режиме ведущего (master) и ведомого (target) с поддержкой основной адресации (7 бит) и расширенной (10 бит). При наличии нескольких ведущих на шине выполняется штатная арбитрация.

## Контроллер интерфейса QSPI

Контроллер QSPI (Serial Peripheral Bus) является контроллером загрузочного ПЗУ. По включению питания осуществляет протокол загрузки, совместимый с обычным SPI.

Контроллер реализует режим ведущего. Включает DMA-контроллер для пакетных передач из/в память (поток данных сформирован в памяти). Доступен отображенный в память канал чтения из QSPI ведомого с аппаратной реализацией протокола QSPI. Адресуется одно устройство (CS). В адресное пространство процессора отражено прямо адресуемое окно размером в 1 Мбайт.

## Контроллер интерфейса SPI

В микросхеме присутствуют 3 контроллера SPI, функционирующие в режиме ведущего с с выбором до 4 устройств (SPI0 - 4CS, SPI1 – 4 CS, SPI2 – 1CS). Включает DMA-контроллер для пакетных передач из/в память. В адресное пространство процессора отражено прямо адресуемое окно размером в 16 Мбайт от каждого контроллера.

Программируемая скорость до 12 Мбит/с.

## Контроллер прямого доступа в память

12-канальный контроллер DMA (IDMA) поддерживает передачи память-память, память-ЦАП и АЦП-память, память — UART в обе стороны. Задавать передачу можно как с использованием цепочки дескрипторов, так и в регистрах.

## Контроллер интерфейса CAN

В микросхеме присутствуют 2 контроллера, поддерживающие протокол CAN 2.0A/В с программируемой скоростью передачи информации до 1 Мбит/с; стандартный/расширенный тип сообщений; удаленный запрос данных; 32 независимых буфера, работающих либо на приём, либо на передачу; аппаратную фильтрацию принимаемых сообщений для каждого приёмного буфера отдельно; режима автоответа при удалённом запросе; режим самотестирования.

#### МИКРОКОНТРОЛЛЕР КОМДИВ-МК К5500ВК018

## Контроллер интерфейса USB

Контроллер USB для встроенных применений представляет собой Host-контроллер интерфейсов USB 2.0 и USB 1.1. Для связи с приёмопередатчиками USB используется интерфейс ULPI.

#### Блок АЦП

Блок АЦП предназначен для измерений и контроля напряжений внешних и внутренних датчиков. Внешних каналов — 8, внутренних — 3, разрядность — 12 бит. Скорость выборок — не менее 50 в секунду. Поддерживаются следующие режимы:

- режимы преобразования: однократный режим, режим сканирования, прерывистый режим;

- унитарный и дифференциальный режим измерения с усреднением или без усреднения измеряемых параметров;

- режим автокалибровки для автоматической подстройки шкалы измерений;

- программный запуск измерений или автоматический запуск по событиям от таймеров или внешнего сигнала;

- режим экономичного энергопотребления с отключением блока АЦП

Блок АЦП включает индивидуальные цифровые компараторы на каждый канал измерений и внутренний буфер измерений с возможностью DMA-передачи измерений «контроллер-память».

Блок также позволяет измерять внутренние параметры микросхемы, такие как температуру и напряжения.

#### Блок ЦАП

Контроллер ЦАП предназначен для выставления заданного уровня напряжения относительного опорного на выводах микросхемы. Контроллер ЦАП реализует 4 аналоговых канала. Разрядность канала составляет 14 бит, частота выставления кодов — до 500 кГц. Поддерживаются 2 режима работы ЦАП: статический, с заданием значением в регистре, и DMA — требуемый уровень напряжения задаётся списком значений в памяти.

## Host-контроллер SDHC/SDIO

Контроллер внешних устройств SDIO пригоден для построения высокоскоростных сетевых средств защиты с функциями криптографической защиты и совместим со спецификациями "SD Host controller Standard Specification Version 4.2", "SD Physical Layer Version 3.01", "MMC Specification Version 4.5". Поддерживает 1- и 4-разрядные интерфейсы SDIO, сигналы детектирования карты и защиты от записи, прерывания и режимы передачи ADMA2. Контроллер позволяет вычислять CRC для данных и команд, программировать частоту тактового сигнала для SDIO. Внутренняя буферная память размером 2 кбайта определяет максимальный размер блока данных. Есть возможность детектирования таймаута при передачах.

#### Контроллер часов реального времени RTC

Контроллер RTC предназначен для отсчета реального времени, содержит 100 летний (2000-2099 гг.) Григорианский календарь (год, месяц, день и день недели) с учетом високосных годов. Время с точностью до секунды представлено в 24-часовом формате (часы, минуты, секунды). Минимальное программно-видимое разрешение часов 500 мс. Имеется встроенный однократный/регулярный будильник. Возможна цифровая подстройка точности хода часов.

#### Блок квадратурного декодера

Квадратурный декодер преобразует цифровой сигнал с датчика положения вала, позволяя вычислять скорость, направление вращения, а также текущее положение вала. Содержит антидребезговый фильтр.

## Блок разовых команд GPIO

Блок разовых команд содержит 48 управляющих линий ввода-вывода, разделённых на 6 портов. Все 8 линий каждого порта могут быть использованы на выход в качестве управляющих сигналов и выставлять прерывание по изменению уровня входного сигнала.

Предусмотрены фильтрация дребезга на входе порта, защёлкивание временной метки события на входе порта.

## Контроллер внутрисхемной отладки ЕЈТАС

Контроллер EJTAG обеспечивает отладочный режим (Debug Mode), загрузку ПО по JTAG, возможность остановки ядра по команде из отладчика, возможность чтения памяти DDR и архитектурно-видимых регистров в режиме отладки, возможности выполнения пошаговой отладки ПО в исходных кодах (языках C, C++) при помощи отладчика (требуется поддержки со стороны ПО отладчика).

## Блок управления режимами энергосбережения

Блок предназначен для программного отключения тактовой частоты не-используемых блоков микроконтроллера.

# Документация

Технические условия (ТУ)

Справочный лист (Д1)

Указания по применению (Д4)

Описание системы команд (Д6)

Схема электрическая структурная (Э1)

Габаритный чертеж (ГЧ)

# Программное обеспечение

Программирование микроконтроллера осуществляется на языке С для работы в среде операционной системы реального времени ОС РВ Багет 2.6. Инструментальное кросс-средство программирования Си-компилятор СКРВ Багет 3.3 функционирует на инструментальной ЭВМ в среде ОС Linux. Для отладки программ применяется отладчик ОРВ 2.6.

Для микроконтроллера K5500BK018 разработаны библиотеки программ, работающие в среде ОС РВ Багет 2.6 и обеспечивающие работу со специализированными протоколами:

- Modbus RTU

- Modbus TCP

- MЭК 60870-5-101

- MЭК 60870-5-104

- OPC UA

Возможна также разработка программ для работы в среде ОС Linux, функционирующей на микроконтроллере.

# Аппаратные средства разработки

Программируемый логический контроллер ПЛК «Багет-ПЛК1-01» ЮКСУ.421457.002-01 на базе микроконтроллера К5500ВК018 применяется в качестве отладочной платы для разработки программного обеспечения и освоения возможностей микроконтроллера.

On-line заказ изделий <a href="https://www.niisi.ru/zakaz.htm">https://www.niisi.ru/zakaz.htm</a>

## Структурная схема микроконтроллера

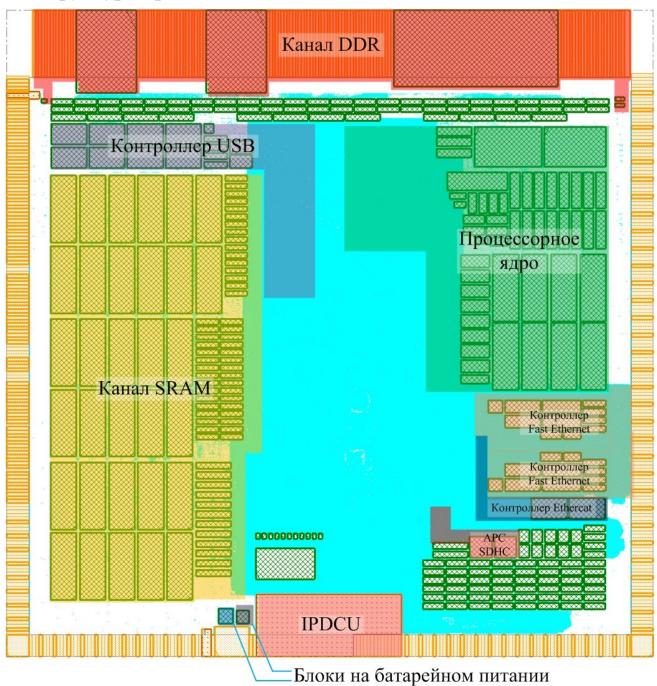

## Структура кристалла

Дополнительная информация:

117218, Москва, Нахимовский проспект, 36, к.1

niisi@niisi.msk.ru https://www.niisi.ru